RISCとCISC

- RISC (Reduce :減らす、縮小)

単純な命令のみに絞ったCPUです。単純な命令なので処理の高速化が期待できる。

使用例:組み込み(家電など) - CISC (Complex :複合、複雑)

単純なものから複雑な命令まで種類を増やしていて、1命令で色々できるCPUである。

使用例:パソコン、サーバ

RISCはワイヤードロジック方式(ハードウェア的)

CISCはマイクロプログラム方式(ソフトウェア的、小さなプログラムをいっぱい)を採用している。

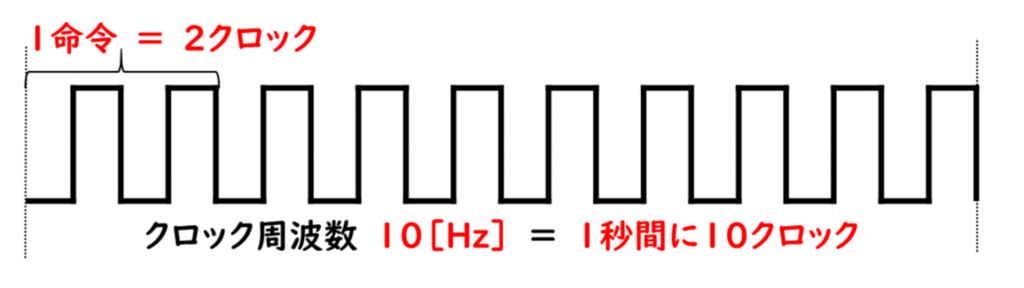

クロック周波数とCPI

クロック周波数のイメージは

「1秒間のCPUのリズム」である。単位は「Hz」

CPIとは

Cycles(一周) Per(ごと) Instruction(命令) の略であり、1命令を実行するときに要するクロック数である。

上記の画像のように、クロック周波数が10Hzで1命令2クロックの場合、要する時間は普通に考えて

1 / クロック周波数 * クロック数 で求まるため、

1 / 10 * 2 = 0.2 となる。

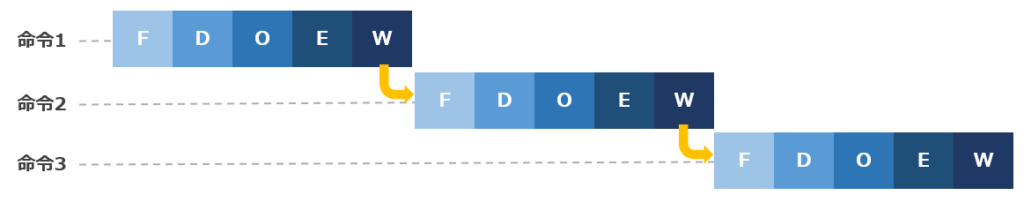

命令パイプライン

CPU(プロセッサ)の性能を向上させるための技術のひとつであり、複数の命令を並行して実行するための方式

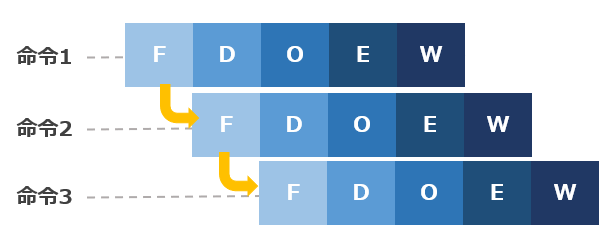

以前も触れたように、命令は、命令フェッチ → デコード → オペラント読出し → 実行(計算) → 結果格納の段階順に実行されていく。

通常は、すべてが終わってから、次の命令を実行していくが

パイプライン処理は、段階で分けて並列に処理していく

ハザード

パイプランを阻害する現象や障害のこと。命令同士に依存関係が少なからずあるため、並列に処理すればするほど障害が起きる可能性が高まる。

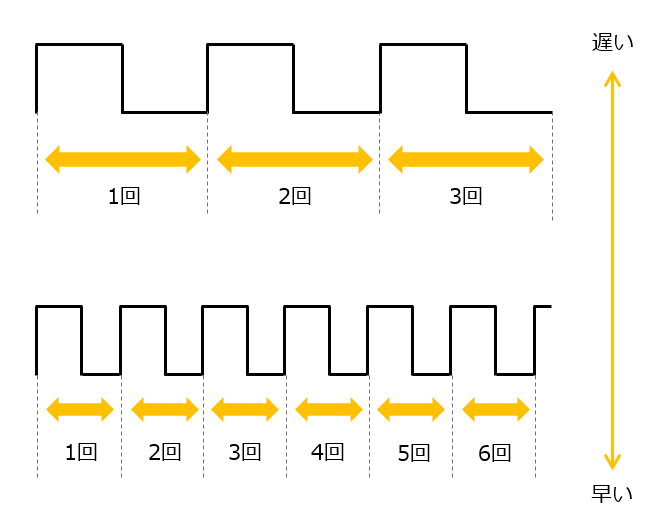

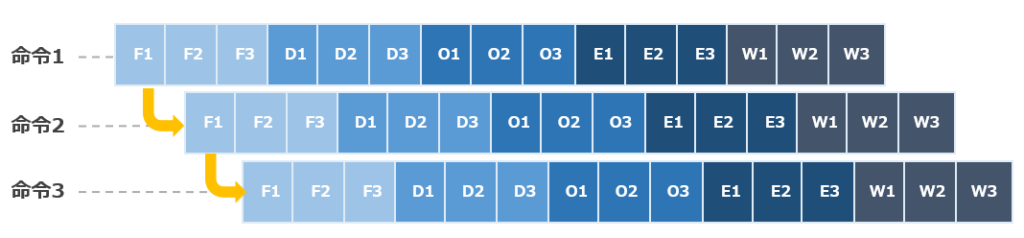

スーパパイプライン

命令の5つの段階(命令フェッチ → デコード → オペラント読出し → 実行(計算) → 結果格納)を細かく分けて、パイプラインよりも多く並列に処理すること

並列に処理すればするほどハザードも多くなるため、結果的には、CPI(1命令に何クロック)は1に近くなる。無限に速くできるわけじゃない。

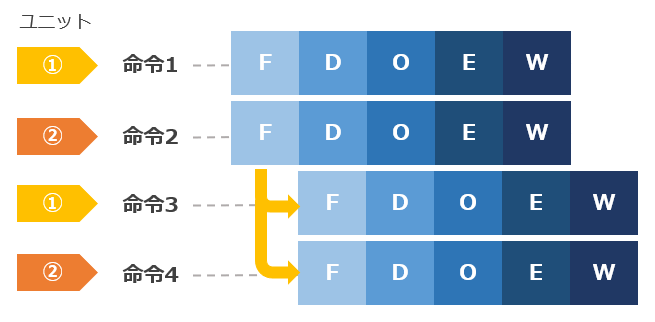

スーパスカラ

パイプラインを実行するユニットを増やして、パイプライン自体を多重化させる。

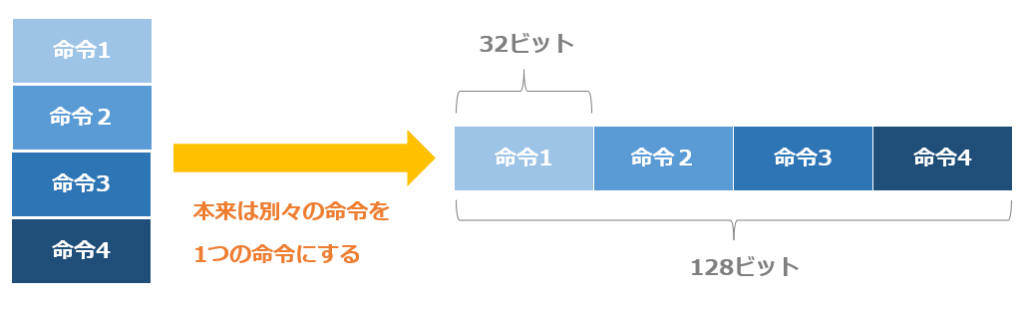

VLIW(very long instruction word)

独立した命令(ほかの命令に依存しない命令)を集めて、長い命令(very long istruction)にまとめる。

依存関係がないため、長い命令を複数個作って、複数個の実行ユニットに並列(同時)で処理させることもできる。