主記憶装置のアクセス時間

主記憶装置にアクセス(読み書き)するときの時間を求める。

主に2つの動作が必要であり、主記憶の中の位置を定める(アドレス選択)、読み書きするデータを転送する(データ転送)がある。

アドレス選択時間 + データ転送時間 = アクセス時間

プロセッサ(CPU)と主記憶の速度差で効率が悪くなることを「ボトルネック」という。よって、速度差を埋める工夫が必要になるのだ。

誤り制御

コンピュータは人々が思うほど正確でなく、間違うことがある。よって誤りを制御する仕組みが必要となる。主記憶装置には誤りを検出・訂正する必要がある。

大きく、パリティチェックとハミング符号方式

パリティチェック

データに対してパリティビットと呼ばれる検査用のビットを追加することで誤りを検知する方法

特徴:1ビットの誤りを検出できる。

ハミング符号方式

複数のチェックコード(ハミング符号)を付けることで2ビット以上の誤り検知を行えるようにする方法

特徴:1ビットの検出・訂正 / 2ビット検出

ECCメモリがハミング符号方式を使っている

高速化

キャッシュメモリ方式とメモリインタリーブ方式がある。

キャッシュメモリ方式

CPUと主記憶の速度差を埋めるために、間にキャッシュメモリを置く方式。

高速なキャッシュメモリによく使うデータを置いて、主記憶にそれ以外を入れて、アクセスする時間を短くする。

プロセッサ(CPU)に近い順から、1次キャッシュ、2次キャッシュと名前がつく。

キャッシュメモリの書き込み

書き込むとき、主記憶へ反映する必要がある。

書き込み方は2つあり、ライトスルー、ライトバックがある。

| ライトスルー | 書き込むとき一緒に主記憶に反映する。 |

| ライトバック | 後で主記憶に反映する。 |

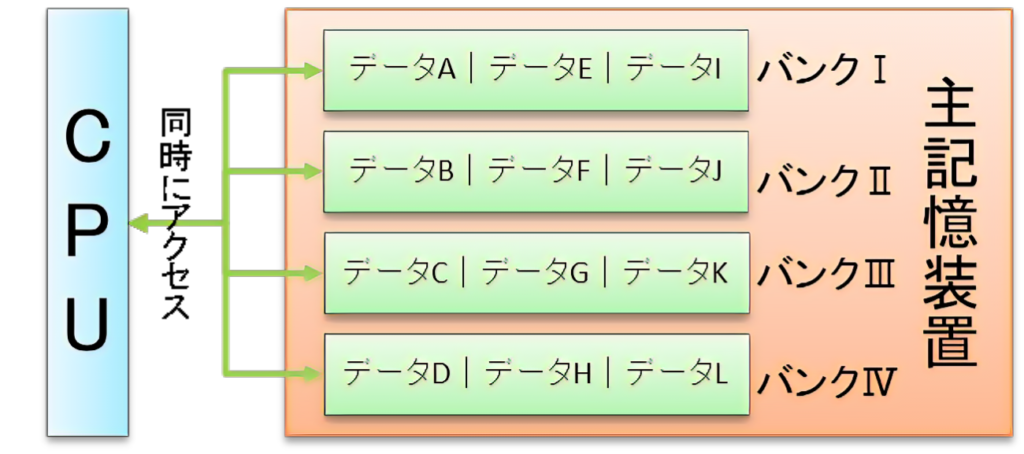

メモリインタリーブ

いくつかのバンク(独立してアクセスできる単位)に分け、並列にアクセスを可能とする方式。

実行アクセス時間(計算)

キャッシュメモリの平均アクセス時間 + 主記憶の平均アクセス時間

ヒット率 * アクセス時間 = 平均アクセス時間

これらのことに注意して実際に解いてみるといい。