構成要素

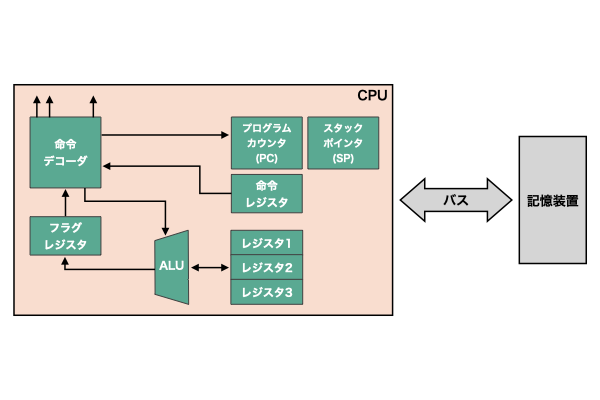

上の画像のようにプロセッサ(CPU)は「バス」で記憶装置とつながっている。

次に、CPUは以下の表に示す装置からなる。

たくさんあるが、とりあえずレジスタはCPUの中にある高速で小さな記憶空間なんだなーでよい。

後に書かれている、処理の例を見ながら一緒に考えるとよい。

1)制御部

| 種類 | 内容 |

|---|---|

| 命令レジスタ | 記憶装置から取り出した命令を格納するレジスタ |

| デコーダ(解読器) | CPUで実行する命令を解読する装置 |

| プログラムカウンタ (プログラムレジスタ) | 実行する命令が保持されている記憶装置のアドレスを格納するレジスタ |

2)演算部

| 種類 | 内容 |

|---|---|

| メモリアドレスレジスタ | 操作の対象となるアドレスを格納するレジスタ |

| 汎用レジスタ | 演算に使用するデータを格納する汎用的なレジスタ |

| ALU (算術論理演算装置) | 四則演算や論理演算をする装置 |

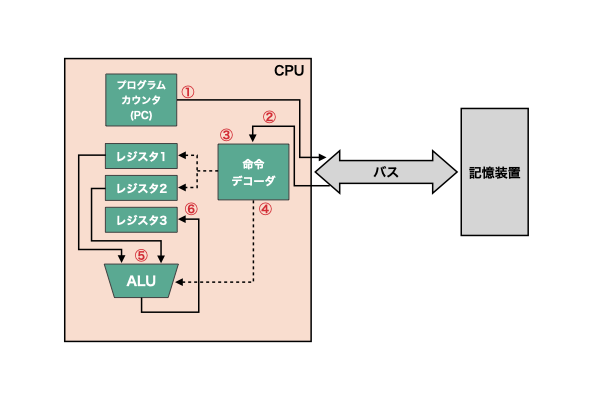

処理の例

| 番号 | 内容 |

|---|---|

| ① | 記憶装置から取り出す命令は、プログラムカウンタの値を参考する。(様々な方法がある) |

| ② | 記憶装置に保存された命令を、実際に取り出す。 |

| ③ | 取り出した命令を解読し、命令の内容を特定する。 |

| ④ | 解読した命令に従って、汎用レジスタと演算器に、加算処理を行うように制御する。 |

| ⑤ | 演算器(ALU)は、レジスタ1と2からデータを取り出して、2つのデータの加算を行う。 |

| ⑥ | 計算結果を、レジスタ3に格納する。 |

以上の1〜6の順序の処理が行われることで、「ある二つの値を加算する処理」を実現することができます。

おおまかな処理の流れを理解できるようにしよう。

補足的に説明すると、

②では、省略されているが、命令を取り出したデータは、命令レジスタに格納される。この操作を命令フェッチという。

④では、命令レジスタに格納されているデータなどで命令を実行するために対象データのアドレス(有効アドレス)を計算し、それを上の画像ではレジスタ(汎用レジスタ)1・2に格納しているんである。この操作が上の図では省略されているが、この操作をオペラント読出しという。

処理の名前を並べると、

命令フェッチ → デコード → オペラント読出し → 実行(計算) → 結果格納

となる。